# Digital On-chip Temperature Sensor with I<sup>2</sup>C Interface

### **Features**

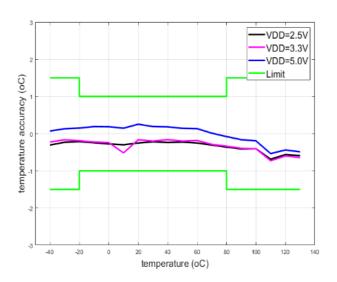

- Temperature accuracy

- $\pm 1^{\circ}$ C(max.) from  $0^{\circ}$ C $\sim 100^{\circ}$ C

- $\pm 2$ °C(max.) from -40°C $\sim 125$ °C

- Low power consumption

- 4.5uA shutdown current at VDD=5.0V

- 125uA continuous conversion current

- 2.5~5.5V ultra-wide operation supply voltage

- High PSR in temperature monitoring

- I2C & SMBus digital communication interface

- LM75 function and register compatible

- 0.0625°C temperature resolution

- Support up to 32 devices by A0/A1/A2 pin hardware configuration

- OS pin open-drain alert and interrupt multi-function

- OS output polarity configuration

- Embedded one-shot conversion mode

- TRIP mode for Hi TEMP and Lo-TEMP detection

## **Applications**

- Home appliance thermal control

- Server board temperature monitoring

- Thermostat control

- Environmental temperature monitoring

- Electronic equipment and facilities

- General system thermal management

## **Description**

The ETS75A is a digital-type high-accurate on-chip integrated temperature sensor chip with an integrated high resolution sigma-delta converter and I2C/SMBus digital interface. It is register and function compatible with industrial standard LM75 digital temperature sensor. ETS75A is available in E-MSOP8 package, it offers hardware pin and firmware compatibility to easy upgrade from LM75x design.

Digital communication 2-wire interface which operates up to 400KHz of fast mode. There are 3 hardware address pins, A0/A1/A2, which could configure the I2C address externally. The

ETS75A a dedicated overhas temperature shutdown output (OS) pin with programmable higher or lower limit in hysteresis. The OS pin could also be output polarity reverse by configure POL register bit setting in configuration register. There is a consecutive fault measurements function which could be programmed 1/2/3/4 counts. The OS pin will enabled if the temperature conversion data is over the pre-set limitation value continuously, and satisfies the FQ[1:0] resister setting.

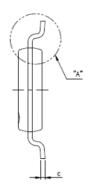

## **Pin Assignments**

# **Pin Description**

|     | Pin  |     | DECCRIPTION                                        |  |

|-----|------|-----|----------------------------------------------------|--|

| No. | Name | I/0 | DESCRIPTION                                        |  |

| 1   | SDA  | I/0 | I2C data pin                                       |  |

| 2   | SCL  | I   | I2C clock input pin                                |  |

| 3   | OS   | 0   | Over-temperature shutdown output (open-drain type) |  |

| 4   | GND  | P   | Ground terminal                                    |  |

| 5   | A2   | I   |                                                    |  |

| 6   | A1   | I   | Device I2C address configuration inputs            |  |

| 7   | A0   | I   | _                                                  |  |

| 8   | VDD  | P   | Power supply terminal                              |  |

# **Ordering Information**

| Product ID     | Package  | Packing / MPQ               | Comments |

|----------------|----------|-----------------------------|----------|

| ETS75A-MT08NNR | EMSOP-8L | Tape & reel / 3000<br>Units | Green    |

# **Marking Information**

Marking Information

Line 1: Product name

Line 2: Date code

## **Absolute Maximum Ratings**

Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device.

| PARAMETER                  | CONDITIONS                                                                                                                    | MIN  | MAX | UNIT |  |  |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--|--|

| Supply voltage             | -0.3                                                                                                                          | 8.0  | V   |      |  |  |

| Input pin voltage          | A0, A1, A2                                                                                                                    | -0.3 | 8.0 | V    |  |  |

| Digital interface          | -0.3                                                                                                                          | 8.0  | V   |      |  |  |

| Output pin voltage         | -0.3                                                                                                                          | 8.0  | V   |      |  |  |

| Operating temperature rang | e                                                                                                                             | -40  | 125 | ۰C   |  |  |

| Junction temperature       |                                                                                                                               |      |     |      |  |  |

| Storage temperature range  | perature range         -40         125           erature         -         150           rature range         -55         150 |      |     |      |  |  |

| Human Body Model           | Human Body Model                                                                                                              |      |     |      |  |  |

| Charged Device Model       | Charged Device Model                                                                                                          |      |     |      |  |  |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| SYMBOL | PARAMETER                              | MIN | MAX | UNIT |

|--------|----------------------------------------|-----|-----|------|

| VDD    | Supply voltage                         | 2.5 | 5.5 | V    |

| TA     | Operating free-air ambient temperature | -40 | 125 | ۰C   |

## **Thermal Information**

| Package Type | Device No. | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) | Exposed Thermal Pad |

|--------------|------------|------------------------|------------------------|---------------------|

| EMSOP-8L     | ETS75A     | 40                     | 10                     | (Note 1)            |

Note 1.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB's ground plane is necessary.

Note 1.3:  $\theta_{lC}$  represents the thermal resistance for the heat flow between the chip junction and the package's top surface. It's extracted from the simulation data with obtaining a cold plate on the package top.

All voltage values are with respect to network ground terminal.

<sup>(3)</sup> Power dissipation and thermal limits must be observed.

Note 1.2:  $\theta_{JA}$  is simulated on a room temperature ( $T_A=25$ °C), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The measurement is simulated using the JEDEC51-5 thermal measurement standard.

## **Electrical Characteristics**

• VDD= $2.5\sim5$ V, at T<sub>A</sub>= $-40\sim125$ °C, unless otherwise noted

| SYMBOL          | PARAMETER                       | CONDITION                | MIN    | TYP    | MAX    | UNIT |

|-----------------|---------------------------------|--------------------------|--------|--------|--------|------|

| VDD             | Supply voltage                  | Normal operation         | 2.5    | _      | 5.5    | V    |

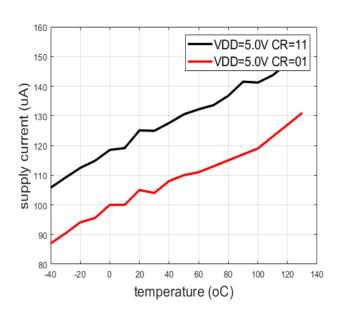

| Io              | Quiescent supply                | RC[1:0]=11               | _      | 125    | 200    | uA   |

| IQ              | I <sub>Q</sub> Quiescent supply | RC[1:0]=10/01/00         | _      | 105    | 150    | uA   |

| $I_{SD}$        | Shutdown current                | VDD=5.0V                 | _      | 4.5    | _      | uA   |

| 130             | Shutdown current                | VDD=3.3V                 | _      | 4.0    | _      | uA   |

|                 |                                 | Temperature Data         | _      |        |        |      |

|                 | Temperature range               | _                        | -40    | _      | 125    | °C   |

|                 | Accuracy                        | 0~100°C                  | _      | ±0.5   | ±1     | °C   |

|                 | recuracy                        | -40~125°C                | _      | ±1     | ±2     | °C   |

|                 | Resolution                      | 1LSB                     | _      | 0.0625 | _      | °C   |

|                 | Repeatability                   | 1LSB                     | _      | 0.0625 | _      | °C   |

|                 |                                 | RC[1:0]=11               | _      | 220    | _      |      |

| Convers         | Conversion Time                 | RC[1:0]=10               | _      | 110    | _      | ms   |

|                 | donversion time                 | RC[1:0]=01               | _      | 55     | _      | 1113 |

|                 |                                 | RC[1:0]=00               | _      | 27.5   | _      |      |

|                 | OS mode conversion              | OSM=1                    | _      | 14.4   | _      | ms   |

|                 |                                 | Digital I/O Interface    |        |        |        |      |

| $V_{IH}$        | Input logic high level          | A0, A1, A2 SCL, SDA pins | 0.7VDD | _      | _      | V    |

| V <sub>IL</sub> | Input logic low level           | A0, A1, A2 SCL, SDA pins | _      | _      | 0.3VDD | V    |

| ILEAK           | Leakage current                 | A0, A1, A2 SCL, SDA pins | _      | _      | 0.5    | uA   |

| Vol             | Output logic low level          | I <sub>SINK</sub> = -3mA | _      | 0.15   | 0.4    | V    |

| V OL            | output logic low level          | I <sub>SINK</sub> = -5mA | _      | 0.2    | 0.4    | V    |

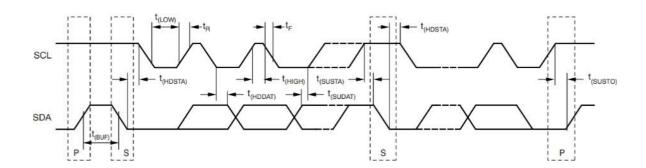

## **Timing Specification**

• VDD=2.5V  $\sim$  5.5V, at T<sub>A</sub>=25°C (unless otherwise noted) (\*1)

| SYMBOL             | CONDITION                                 | MIN  | MAX | UNIT |

|--------------------|-------------------------------------------|------|-----|------|

| $f_{SCL}$          | SCL operating frequency                   | 2.5  | _   | us   |

| $f_{\mathrm{BUF}}$ | Bus free time between STOP and START      | 1.3  | _   | us   |

| thdsta             | Hold time after repeated START condition. | 600  | _   | ns   |

| <b>t</b> susta     | Repeated START condition setup time       | 600  | _   | ns   |

| t <sub>SUSTO</sub> | STOP condition setup time                 | 600  | _   | ns   |

| t <sub>HDDAT</sub> | Data hold time (*2)                       | 0    | _   | ns   |

| thsudat            | Data setup time                           | 100  | _   | ns   |

| tLow               | SCL clock low period                      | 1300 | _   | ns   |

| t <sub>HIGH</sub>  | SCL clock high period                     | 600  | _   | ns   |

| $t_{VDAT}$         | Data valid time (*3)                      | _    | 900 | ns   |

| t <sub>FDA</sub>   | Data fall time                            | _    | 300 | ns   |

| t <sub>R</sub>     | Clock rise time                           | _    | 300 | ns   |

| $t_{\mathrm{F}}$   | Clock fall time                           | _    | 300 | ns   |

| Time out           | Bus release time out                      | 2    | _   | ms   |

| tRCClock/data      | rise time for SCL=100KHz                  | _    | 1   | us   |

- (\*1) The host and device have the same VDD voltage. The voltages are based on statistical analysis of samples tested during initial release.

- (\*2) The maximum  $t_{\text{HDDAT}}$  can be 0.9us for fast mode, and is less than the maximum  $t_{\text{VDAT}}$  by a transition time.

- (\*3) t<sub>VDAT</sub>=time for data signal from SCL LOW to SDA output (HIGH to LOW, depending on which is worst). = time for data signal from SCL LOW to SDA output (HIGH to LOW, depending on which is worse).

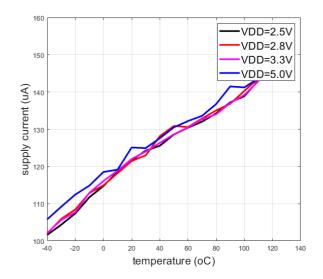

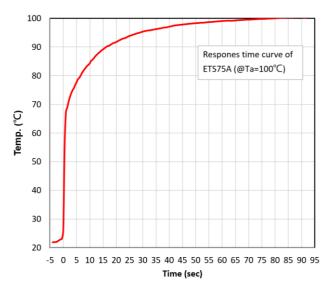

# **Typical Characteristics**

## **Function Description**

#### **Overview**

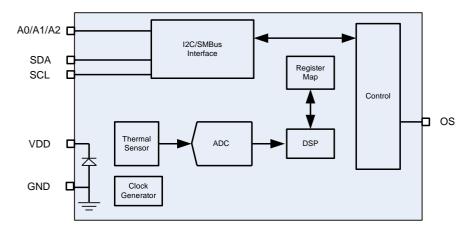

The ETS75A is an on-chip digital temperature sensor which is applicable in environment temperature management and thermal protection. The device is I2C and SMBus interface compatible. The device is specified over a temperature range of -40°C to 125°C. The Block diagram section shows the functional block diagram of ETS75A device.

The temperature sensor thermal path goes through thermal pad on assembly bottom and package leads as well as the plastic package. The thermal path will run by lowest thermal resistance of the assembly.

### **Block Diagram**

Figure 1. EST75A Block Diagram

## **Digital Temperature Output**

The temperature register saves the temperature measurement data from analog-to-digital converter. The register is read-only and contains two 8-bit data bytes consisting of one Upper Byte and one Lower Byte. However, only the first 12 MSBs are used to store the temperature data in 2's complement format with 0.0625°C resolutions while the remaining 4 LSB are set to zero. The MSB bit of the upper byte is a sign bit which used to indicate positive or negative data. Table 1 shows the bit arrangement of the temperature data in the dual-byte register.

|      | Upper Byte |      |      |     |     |     |     |       | Lower By | te      |          |    |    |    |    |

|------|------------|------|------|-----|-----|-----|-----|-------|----------|---------|----------|----|----|----|----|

| T15  | T14        | T13  | T12  | T11 | T10 | Т9  | Т8  | T7    | T6       | T5      | T4       | Т3 | T2 | T1 | T0 |

| sign | 64°C       | 32°C | 16°C | 8°C | 4°C | 2°C | 1°C | 0.5°C | 0.25°C   | 0.125°C | 0.0625°C | 1  | _  | _  | _  |

Table 1. Temperature register

| Temperature | Temperature | Digital Output |                     |  |  |  |

|-------------|-------------|----------------|---------------------|--|--|--|

| (°K)        | (°C)        | Hex Value      | Binary Value        |  |  |  |

| 400.15      | 127         | 7F00           | 0111 1111 0000 0000 |  |  |  |

| 373.15      | 100         | 6400           | 0110 0100 0000 0000 |  |  |  |

| 353.15      | 80          | 5000           | 0101 0000 0000 0000 |  |  |  |

| 348.15      | 75          | 4B00           | 0100 1011 0000 0000 |  |  |  |

| 323.15      | 50          | 3200           | 0011 0010 0000 0000 |  |  |  |

| 298.15      | 25          | 1900           | 0001 1001 0000 0000 |  |  |  |

| 273.4       | 0.25        | 0040           | 0000 0000 0100 0000 |  |  |  |

| 273.2125    | 0.0625      | 0010           | 0000 0000 0001 0000 |  |  |  |

| 273.15      | 0           | 0000           | 0000 0000 0000 0000 |  |  |  |

| 273.0875    | -0.0625     | FFF0           | 1111 1111 1111 0000 |  |  |  |

| 272.9       | -0.25       | FFC0           | 1111 1111 1100 0000 |  |  |  |

| 248.15      | -25         | CE00           | 1110 0111 0000 0000 |  |  |  |

| 233.15      | -40         | D400           | 1101 1000 0000 0000 |  |  |  |

Table 2. Temperature Data Format

Note1: For 9-bit temperature data ism compatible with LM75, just use only 9 MSB bits of the Upper Byte in the two bytes and disregard 7 LSB bits of the Lower Byte. The 9-bit temperature data with 0.5 resolution of the device is defined exactly in the same way as for the standard LM75.

$Note 2: User could \ read \ the \ required \ temperature \ resolution \ data \ in \ specified \ application \ even \ 1^{\circ}C \ resolution \ is \ allowed.$

Note3: The MSB bit of the temperature data is dedicated for Sign-bit to indicate the positive temperature or negative temperature. The temperature data is stored in 2's complement data format.

#### **I2C and SMBus Serial Interface**

The ETS75A can be connected to a compatible 2-wire serial interface as a slave device under a controller or master device. Connections to the bus are made through the open-drain I/O line SDA and SCL input pin. External pull-up resistor is needed for each of the two terminals. There are Schmitt triggers at SDA/SCL input signal chain to minimize the effects of signal fluctuations and bus noises. The ETS75A supports the I2C transmission protocol up to 400KHz clock frequency of fast mode.

### **I2C Bus Overview**

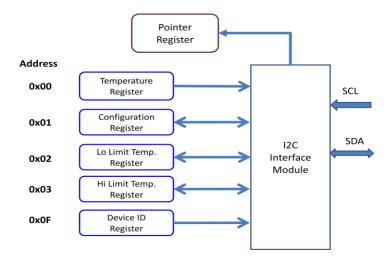

The data register in the ETS75A are selected by Pointer register. At power-up, the Pointer Register is set to 0x00. Each data register falls into one of three types of user accessibility, (a) Read Only (b) Write only (c) Write/Read same address.

A write command to this device will always include the address byte and the pointer byte. A write to any register other than the Pointer register requires two data bytes.

### **Bus Fault Timeout**

The ETS75A supports SMBus timeout feature. If the host holds the SCL pin in "L" more than 2ms(typ.) between a START and STOP condition, the ETS75A would reset its internal state machine to prevent a system bus hang-up. This feature is turned on by default and release SDA and waits for a START condition.

## **Slave Address**

To communicate with the ETS75A, the master device must first address devices through a 7-bit device address, a direction bit indicating the intent of executing a read or write operation. The ETS75A features 3 external hardware address pins to allow up to 32 devices to be addressed on a single serial I2C bus interface. Table 3 shows the pin setting can connect up to 32 devices. The A0, A1 and A2 pins are samples on every bus communication and must be set prior to any activity on the interface. The default value at power-up is 0x00.

| A2 | A1  | A0  | Slave Address   |

|----|-----|-----|-----------------|

| 0  | 0   | SDA | 1000000 (0x40)  |

| 0  | 0   | SCL | 1000001 (0x41)  |

| 0  | 1   | SDA | 100 0010 (0x42) |

| 0  | 1   | SCL | 100 0011 (0x43) |

| 1  | 0   | SDA | 100 0100 (0x44) |

| 1  | 0   | SCL | 100 0101 (0x45) |

| 1  | 1   | SDA | 100 0110 (0x46) |

| 1  | 1   | SCL | 100 0111 (0x47) |

| 0  | 0   | 0   | 1001000 (0x48)  |

| 0  | 0   | 1   | 1001001 (0x49)  |

| 0  | 1   | 0   | 1001010 (0x4A)  |

| 0  | 1   | 1   | 1001011 (0x4B)  |

| 1  | 0   | 0   | 1001100 (0x4C)  |

| 1  | 0   | 1   | 1001101 (0x4D)  |

| 1  | 1   | 0   | 1001110 (0x4E)  |

| 1  | 1   | 1   | 1001111 (0x4F)  |

| 0  | SDA | SDA | 101 0000 (0x50) |

| 0  | SDA | SCL | 101 0001 (0x51) |

| 0  | SCL | SDA | 101 0010 (0x52) |

| 0  | SCL | SCL | 101 0011 (0x53) |

| 1  | SDA | SDA | 101 0100 (0x54) |

| 1  | SDA | SCL | 101 0101 (0x55) |

| 1  | SCL | SDA | 101 0110 (0x56) |

| 1  | SCL | SCL | 101 0111 (0x57) |

| 0  | SDA | 0   | 101 1000 (0x58) |

| 0  | SDA | 1   | 101 1001 (0x59) |

| 0  | SCL | 0   | 101 1010 (0x5A) |

| 0  | SCL | 1   | 101 1011 (0x5B) |

| 1  | SDA | 0   | 101 1100 (0x5C) |

| 1  | SDA | 1   | 101 1101 (0x5D) |

| 1  | SCL | 0   | 101 1110 (0x5E) |

| 1  | SCL | 1   | 101 1111 (0x5F) |

Table 3. Device addresses definition

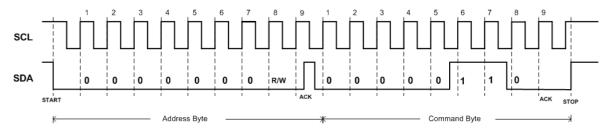

## **General Call Reset Function**

The ETS75A responds to the two-wire general call address (0000 000) if the LSB bit is 0. The device acknowledges the general call address and responds to commands in the  $2^{nd}$  byte. If the  $2^{nd}$  byte is 0000 0110, the ETS75A resets the internal registers to the power-up reset values.

Figure 2. SMBus Timing diagram for General call

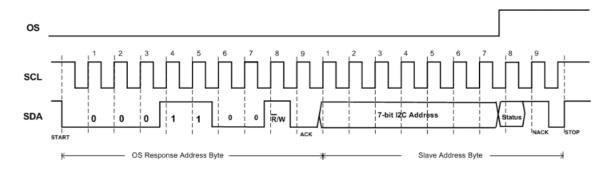

### **SMBus Alert Function**

The ETS75A supports the SMBus Alert function. When the ETS75A is operating in interrupt mode, the OS pin of the ETS75A can be connected as a SMBus Alert signal. When the host senses that an alert condition is present on the OS, the host sends a SMBus Alert command on the bus. If the OS pin of the ETS75A is active, the devices acknowledge the SMBus Alert command and respond by returning the device address on the SDA line. The LSB bit of the device address byte indicates if the temperature exceeding  $T_{HIGH}$  or falling below  $T_{LOW}$  caused the alert condition. This bit is equal to POL if the temperature is greater than or equal to  $T_{HIGH}$ . The bit is equal to /POL if the temperature is less than  $T_{LOW}$ . The timing diagram shows in Figure 3as below.

If multiple devices on the bus respond to the SMBus OS command, arbitration during the device address portion of the SMBus OS command determines which device clears the alert status. If the ETS75A wins the arbitration, the OS pin becomes inactive at the completion of the SMBus OS command. If the ETS75A loses the arbitration, the OS pin remains active.

Figure 3. SMBus Timing diagram for OS Function

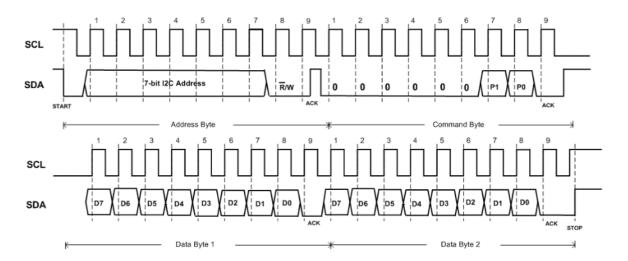

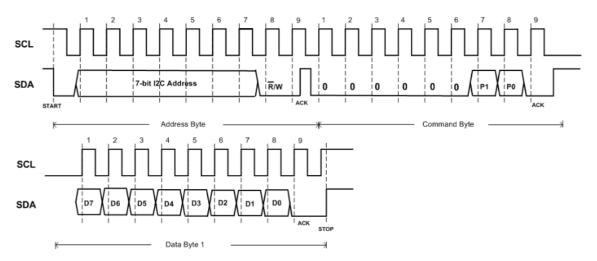

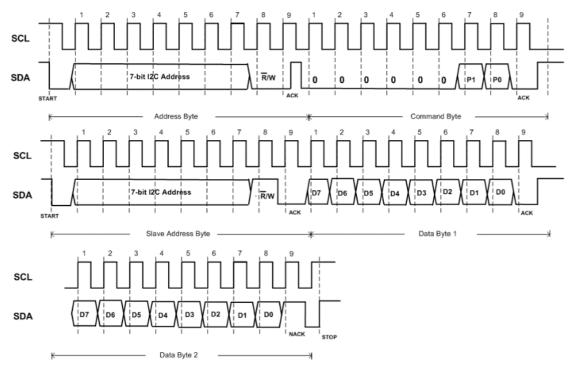

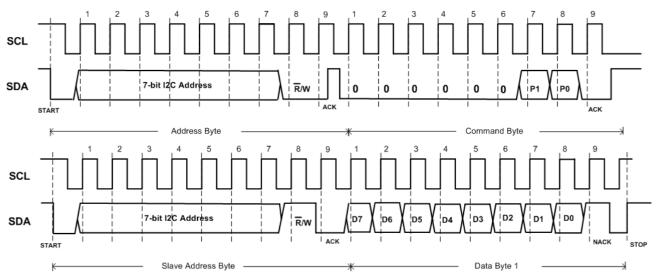

## **Timing Diagram**

Figure~4.~Two-wire~timing~diagram~for~Write~Two~Bytes~format

Figure 5. Two-wire timing diagram for Write Single Byte format

Figure 6. Two-wire timing diagram for Read Two Bytes format

Figure 7. Two-wire timing diagram for Read Single Byte format

### **Operation Mode**

A write to the ETS75A will always include the address byte and the Pointer byte. A write to the Configuration register and limit register requires two data bytes.

Reading the ETS75A can take place in two ways. If the location latched in the Pointer register is correct, then the read can simply consist of an address byte, followed by retrieving the corresponding number of data bytes. If the Pointer register needs to be set, then an address byte, pointer byte, repeat start, and another address byte will accomplish a read. The first data byte is the most significant byte with MSB first, permitting only as much data as necessary to be read to determine temperature condition. At the end of a read, the ETS75A can accept either Acknowledge or No Acknowledge from the master device.

## **Function Mode**

#### **Continuous conversion Mode (CC)**

When system power-on, the ETS75A operates in continuous conversion mode. The configuration register initial value is 0x6000. The temperature data will update continuously after every data conversion. The conversion rate is set by RC[1:0] in configuration register. Every conversion cycle consists of an active conversion followed by a standby period.

#### Shutdown Mode (SD)

The ETS75A can enter shutdown mode if the SD bit in configuration register is set to logic 1. In shutdown mode, all the internal circuit will be disabled and the current consumption will be 4uA (typ.) and the temperature conversion stops. The I2C bus interface remains active and register read/write operation can be performed. When the SD bit is set, the OS output is unchanged in comparator mode and reset in interrupt mode.

### One-shot Mode (OS)

One-shot mode should be enabled when ETS75A stays in shutdown mode. User could initiate the one-shot mode before Bit[0]=1 of High-Byte of configuration register. Setting the Bit[7] of High-Byte in Configuration register, OSM, enables the one shot mode. When this mode is enabled, the ETS75A will initiate a temperature conversion once then goes immediately into shutdown mode. After the temperature conversion, the OS pin will be active for master device interruption. The OSM bit will be cleared to logic 0 after a read operation. The temperature conversion will be initiated if the OSM bit setup again. One-shot mode is useful to reduce power consumption in the ETS75A when continuous temperature monitoring is not required.

#### Thermostat Mode

The thermostat mode can configure the OS pin operates in comparator mode (TM=0) or interruption mode (TM=1). The thermostat mode set by the Bit 1 of Lower Byte of configuration register. Any write to the TM bit will clear the faults count, alert interrupt history and the OS pin will turn to inactive condition.

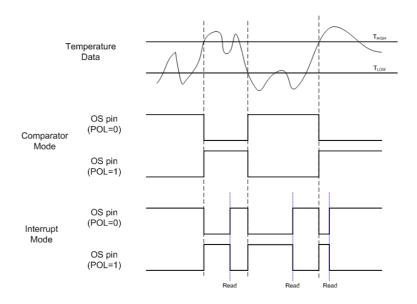

The main difference between the two modes is that in OS comparator mode, the OS output becomes active when temperature data has exceeded THIGH and reset when temperature data has dropped below TLOW, reading a register or putting the device into shutdown mode does not change the stat of the OS output. While in interrupt mode, once it has been activated either by exceeding T<sub>HIGH</sub> or descending below T<sub>LOW</sub>, the OS output remains

Publication Date: Jan. 2023 Revision:1.1 13/23

active indefinitely until reading a register, then the OS output will be cleared.

#### Comparator Mode (TM=0)

In comparator mode, the OS pin becomes active when the temperature equals or exceeds the Thigh for a consecutive number of Fault Queue bits FQ[1:0]. The OS pin remains active until the temperature falls below the T<sub>LOW</sub> value which OS pin toggles back immediately without fault counts. The Fault Queue prevents false alert as a result of system noise.

#### Interrupt Mode (TM=1)

In interrupt mode, the device starts to compare temperature readings with the Thigh register value. The OS pin becomes active when the temperature equals or exceeds THIGH for a consecutive number conversions which set by FQ[1:0].

The OS pin condition in interrupt mode will be cleared by 2 conditions, a read of any register, or a successful SMBus Alert response. After the OS pin is cleared, the device starts to compare temperature readings with the TLOW. As the same, the OS pin will active again only when the temperature drops below TLOW.

Figure 8. OS pin output transfer function in Interrupt mode and comparator mode (T\_TRIP=0)

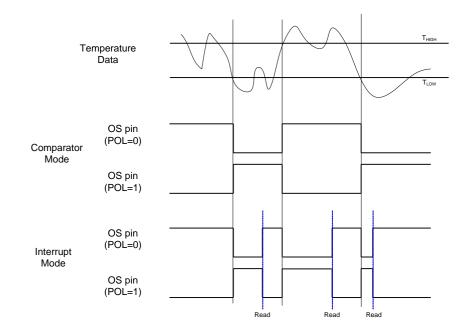

### TRIP Mode (T\_TRIP=1)

In temperature trip mode, OS acts as temperature alert function which is reverse from T\_TRIP=0. In TRIP mode, there are comparator mode and interrupt mode as T\_TRIP=0.

In comparator mode, when the environment temperature decrease under the T<sub>LOW</sub> limit value, and counts to FQ[1:0] times, the OS pin will active Low to alert system. If the temperature ramps up equal to or exceeds THIGH limit value, the OS pin will release the alert signal and return to High level.

In interrupt mode, the device starts to compare temperature readings with the T<sub>LOW</sub> register value. The OS pin becomes active when the temperature equals or drops below TLOW for a consecutive number

conversions which set by FQ[1:0]. The OS pin condition in interrupt mode when T\_TRIP=1 will be

cleared by 2 conditions. In cases of a reading of any register, or a successful SMBus Alert response will release the OS pin in interrupt mode. After the OS pin is cleared, the device starts to compare temperature readings with the Thigh. If the temperature rises equal to or exceeds Thigh limit value, the OS pin will release the alert signal and return to High level.

$Figure \ 9. \quad OS \ pin \ output \ transfer \ function \ in \ Interrupt \ mode \ and \ comparator \ mode \ (T\_TRIP=1)$

#### OS pin output and polarity

The OS pin is an open-drain output and its state represents results of the device watchdog operation. In order to observe this output state, an external pull-up resistor is needed. The resistor should be as large as possible to minimize the temperature data reading error due to internal heating by higher sinking current on OS pin.

The default state of OS pin is active low. If the Bit[2] in Lower byte of configuration register set to 1, the OS pin operation state will change to active high. At power-up, Bit POL will reset to logic0 and the OS pin active state is LOW.

#### **Fault Queue**

The fault queue value can be programmed in FQ[1:0] in configuration register. Fault queue defines the number of faults that must occur consecutively to activate the OS output. It prevents from false tripping due to system noise or temperature fluctuation. Table XX shows the relationship between register set data and fault queue values.

| F | Q[1:0] | Fault queue value |

|---|--------|-------------------|

| 0 | 0      | 1                 |

| 0 | 1      | 2                 |

| 1 | 0      | 3                 |

| 1 | 1      | 4                 |

Table 4. Fault Queue Configuration

### **Pointer Register**

The following diagram shows the internal register structure of ETS75A. There are 4 data registers and 1 device ID register in ETS75A. The pointer address, read/write capability and reset default value at power-up are shown in Table 5. The pointer register at power-up is set to 0x00. The Temperature register and Device ID register are Read-only, others are Read/Write capability. In interrupt mode, a read from the ETS75A, or placing the device in shutdown mode, the OS pin output will be reset.

| Default | P7 | P6 | P5 | P4 | Р3 | P2 | P1     | P0      |

|---------|----|----|----|----|----|----|--------|---------|

| 00x00   | 0  | 0  | 0  | 0  | 0  | 0  | Regist | er bits |

| P1 | P0 | Register Description             |

|----|----|----------------------------------|

| 0  | 0  | Temperature (Read Only) Default  |

| 0  | 1  | Configuration (Read/Write)       |

| 1  | 0  | Lower limit temperature setting  |

| 1  | 1  | Higher limit temperature setting |

Table 5. Pointer Register Address

### Register Map

The ETS75A supports single-byte and two-byte read/write operation by digital serial interface. It is software compatible with industrial standard LM75 devices

| ADDR | Name     | Length | R/W     | Default  | В7         | В6   | B5     | B4  | В3   | B2  | B1 | В0     |  |

|------|----------|--------|---------|----------|------------|------|--------|-----|------|-----|----|--------|--|

| 0x00 | TEMP     | 2      | R Only  | 0x0000   | TEMP[15:8] |      |        |     |      |     |    |        |  |

| UXUU | Register | Bytes  | K Olliy | UXUUUU   |            | TEME | P[7:4] |     | 0    | 0   | 0  | 0      |  |

| 0x01 | Config.  | 2      | R/W     | 0 <000   | OSM        | RC[  | 1:0]   | FQ[ | 1:0] | POL | TM | SD     |  |

| UXU1 | Register | Bytes  |         | 0x6000   |            |      |        |     |      |     |    | T_TRIP |  |

| 002  | L-Limit  | 2      | D /IAI  | TL[15:8] |            |      |        |     |      |     |    |        |  |

| 0x02 | Register | Bytes  | R/W     | 0x4B00   |            | TL[  | 7:4]   |     | _    | _   | _  | _      |  |

| 0x03 | H-Limit  | 2      | D /M/   | 0x5000   | TH[15:8]   |      |        |     |      |     |    |        |  |

| 0X03 | Register | Bytes  | R/W     | 0x3000   |            | TH[  | 7:4]   |     | _    |     |    | _      |  |

Table 6. Register Mapping Definition

#### **Temperature Register**

The Temperature Register is a 12-bit read-only register. The data is represented by 12-bit 2's complement format, the MSB of the Upper byte is a sign-bit. The first MSB 12 bits indicate the junction temperature conversion data and the last 4 LSB bits equal to 0. The Temperature Register default value is 0x00 at power-up.

| Address | W/R    |        | Default | В7         | В6   | B5     | B4 | В3 | B2 | B1 | В0 |

|---------|--------|--------|---------|------------|------|--------|----|----|----|----|----|

| 0**00   | D Only | U Byte | 0x00    | TEMP[15:8] |      |        |    |    |    |    |    |

| 0x00    | R-Only | L Byte | 0x00    |            | TEME | P[7:4] |    | 0  | 0  | 0  | 0  |

Table 7. Temperature Register

#### **Configuration Register**

The Configuration Register is a 16-bit read/write register used to control the operation mode of temperature sensor device. Read and Write operation are performed MSB first. The default value of Configuration Register is 0x6000.

| Address | W/R        |        | Default | В7  | В6  | B5   | B4  | В3   | B2  | B1 | В0     |

|---------|------------|--------|---------|-----|-----|------|-----|------|-----|----|--------|

| 001     | 0.01 P.O.1 | U Byte | 0x60    | OSM | RC[ | 1:0] | FQ[ | 1:0] | POL | TM | SD     |

| 0x01    | R-Only     | L Byte | 0x00    | 0   | 0   | 0    | 0   | 0    | 0   | 0  | T TRIP |

Table 8. Configuration Register

#### **Low Limit Temperature Register**

Low Limit Temperature Register is a 12-bit read/write register. The data is represented by 12-bit 2's complement format. The default value of the low limit temperature register at power-up is 0x4B00.

| Address | W/R |        | Default | B7      | В6       | B5 | B4 | В3 | B2 | B1 | В0 |

|---------|-----|--------|---------|---------|----------|----|----|----|----|----|----|

| 002     | W/D | U Byte | 0x4B    |         | TL[15:8] |    |    |    |    |    |    |

| 0x02    | W/R | L Byte | 0x00    | TL[7:4] |          |    | _  | _  | _  | _  |    |

Table 9.

Low Limit Temperature Register

#### **High Limit Temperature Register**

High Limit Temperature Register is a 12-bit read/write register. The data is represented by 12-bit 2's complement format. The default value of the high limit temperature register at power-up is 0x5000.

| Address | W/R      |        | Default              | В7      | В6 | B5 | B4 | В3 | B2 | B1 | В0 |

|---------|----------|--------|----------------------|---------|----|----|----|----|----|----|----|

| 002     | W/D      | U Byte | J Byte 0x50 TU[15:8] |         |    |    |    |    |    |    |    |

| 0x03    | 0x03 W/R |        | 0x00                 | TU[7:4] |    |    |    | _  | _  | _  | _  |

Table 10. High Limit Temperature Register

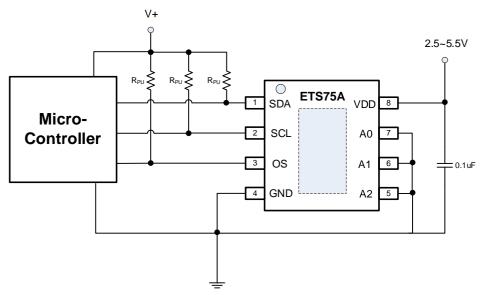

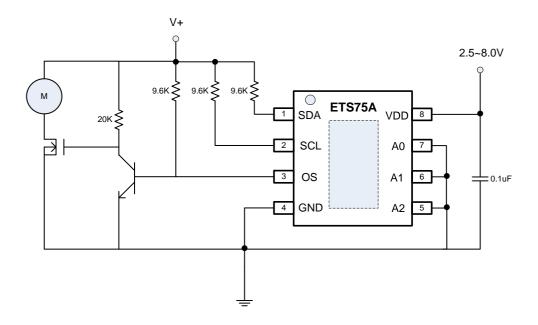

### **Application Circuits**

The ETS75A is a temperature sensor IC which monitors the PCB or environment temperature of the location where user mounts the device. The A2, A1 and A0 pins could connect up to 32 devices on the same I2C serial bus interface. SDA and SCL is a standard I2C and SMBus protocol in open-drain output with external pull-up resistors. The OS pin will interrupt or alarm master device if the monitoring temperature data over or under the pre-set limit value. The OS pin is an open-drain output with external pull-up resistor. The pull-up resistor design should be tradeoff by speed and power consumption requirements.

A 0.1uF bypass capacitor places between VDD and GND is required for power supply noise filtering, see Figure 11.

The SDA, SCL and OS pin should pull-up to a voltage which could be higher than VDD of ETS75A. If the OS pin is not used, it can either be connected to GND or left floating.

Figure 10. ETS75A Application Circuit 1

The ETS75A is designed to be pin-2-pin and functional compatible with industrial standard LM75 family. The two bytes register of the ETS75A dynamically support single byte read or write operation, meaning that it is software compatible with LM75 devices without any firmware updates.

The ETS75A is a temperature sensor device which monitors the environment temperature. The temperature runs through leads and pads under assembly into silicon junction by thermal conduction. The best device placement ensures that temperature changes are captured within the shortest path and time by junction of temperature sensor. A thermally-conductive adhesive is helpful in achieving accurate surface temperature measurement, see Figure 11.

Figure 11. ETS75A Application Circuit 2

The open-drain pull-up resistor could be designed by output driving capability. The minimum pull-up resistor is defined by the sinking current and the maximum output level in equation 1, where VOL (max.) is the maximum logic output low level and IOL is the output sinking current.

$$Rpu(min) = \frac{VDD - V_{OL}(max)}{I_{OL}}$$

(1)

The maximum pull-up resistor is limited by the parasitic capacitance (Cp) and rising time specification of I2C specification. The simplified deduction list in equation 2, where the  $V_{\rm IL}$  is 30% of VDD and  $V_{\rm IH}$  is defined in 70% of VDD.

$$Rpu(max) = \frac{T_{RISE}}{0.85* Cp}$$

(2)

Trise is the rising time of signal waveform from 10% to 90% signal full swing. In I2C specification, the rise time of SDA and SCL signals are specified in different value by different operation mode. For example, in standard mode, the maximum rising time is 1000ns. In high speed mode, if the capacitive load from 10pF to 100pF, the rising time specified in 10ns (min.) and 40ns (max.). If the capacitive load is up to 400pF, the rising time is defined in 20ns (min.) and 80ns (max.).

User could design the pull-up resistor by system requirements, also to compliant to the I2C bus operation mode. One thing needs to be reminded that SDA pin is an open-drain output and SCL is a buffer input.

## **Layout Guidelines**

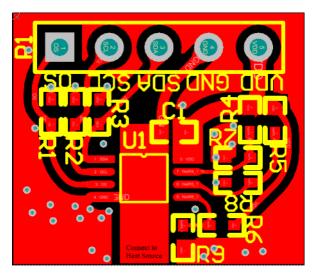

Figure 12. ETS75A EVB Top View

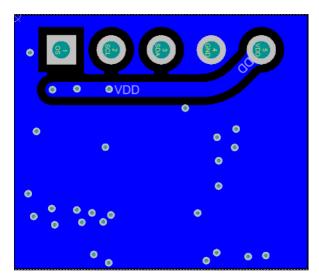

Figure 13. ETS75A EVB Bottom View

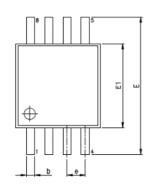

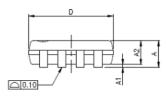

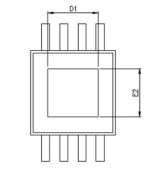

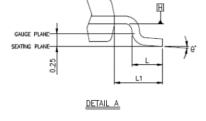

## **Package Dimensions**

# EMSOP-8L(118mil)

THERMALLY ENHANCED VARIATIONS ONLY

| SYMBOLS | MIN.           | NOM.     | MAX. |  |  |  |  |  |

|---------|----------------|----------|------|--|--|--|--|--|

| Α       | ı              | _        | 1.10 |  |  |  |  |  |

| A1      | 0.00           | _        | 0.15 |  |  |  |  |  |

| A2      | 0.75           | 0.85     | 0.95 |  |  |  |  |  |

| Ь       | 0.22           | _        | 0.38 |  |  |  |  |  |

| С       | 0.08           | 0.23     |      |  |  |  |  |  |

| D       | 3.00 BSC       |          |      |  |  |  |  |  |

| Е       |                | 4.90 BSC |      |  |  |  |  |  |

| E1      |                | 3.00 BSC |      |  |  |  |  |  |

| е       |                | 0.65 BSC |      |  |  |  |  |  |

| L       | 0.40 0.60 0.80 |          |      |  |  |  |  |  |

| L1      | 0.95 REF       |          |      |  |  |  |  |  |

| θ*      | 0 – 8          |          |      |  |  |  |  |  |

UNIT : MM

# **Revision History**

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | 2022.10.07 | Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.1      | 2023.01.04 | <ol> <li>Modified Feature item(p1)</li> <li>Modified Description character (p1)</li> <li>Changed Ordering Information table (p2)</li> <li>Modified Electrical Characteristics table voltage condition (p4)</li> <li>Modified Timing Specification table(p5)</li> <li>Added Typical Characteristics figure (p6)</li> <li>Modified note description in Table2. (p8)</li> <li>Modified Operation Mode description (p13~p16)</li> <li>Modified Figure10.(p18)</li> <li>Other misspelling modified and value synchronized in description</li> </ol> |

## **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.